### Assam Textile Institute

Empowering Textile Education

Class 5

## COURSE TITLE = TEXTRONICS COURSE CODE= TT-603

by, **PANKAJ JYOTI DAS**(M.TECH),(ECE)

#### : Latch, Flip Flop and It's Types :

- A flip flop is an electronic circuit with two stable states that can be used to store binary data. The stored data can be changed by applying varying inputs.

- ➤ Flip-flops and Latches are fundamental building blocks of digital electronics systems used in computers, communications and many other types of systems.

- ➤ Flip-flops and latches are used as data storage elements. It is the basic storage element in *sequential* logic.

- ➤ Both **Latches and flip flops** are circuit elements where the output not only depends on the current inputs, but also depends on the previous input and outputs.

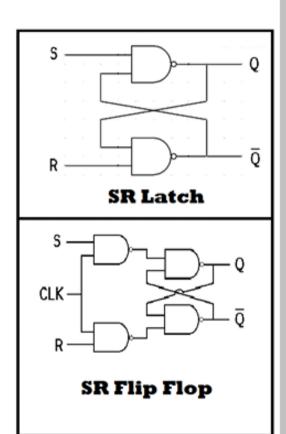

- ➤ The main *difference* between the latch and flip flop is that a flip flop has a *clock signal*, whereas a latch does not have clock signals.

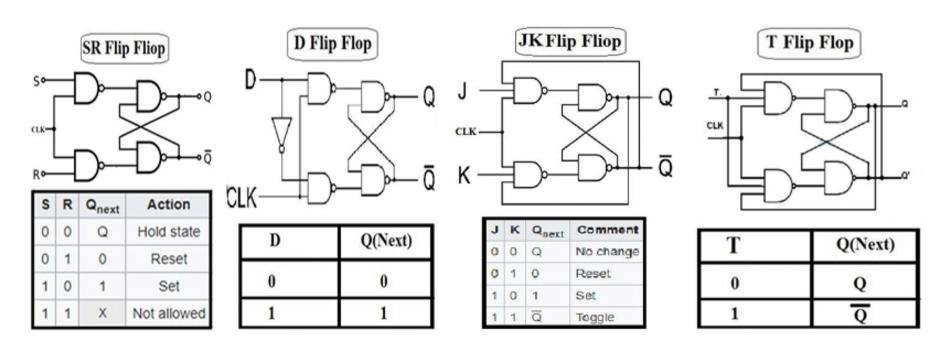

#### :Types of Flip Flop and Truth Tables:

- Flip-flops can be divided into common types: the SR ("set-reset"), D ("data" or "delay"), T ("toggle"), and JK.

- ➤ The behavior of a particular type can be described by what is termed the characteristic equation, which derives the "next" (i.e., after the next clock pulse) output, Q<sub>next</sub> in terms of the input signal(s) and/or the current output.

## :Types of Flip Flop and Truth Tables:

| S | R | Q <sub>next</sub> | Action      |

|---|---|-------------------|-------------|

| 0 | 0 | Q                 | Hold state  |

| 0 | 1 | 0                 | Reset       |

| 1 | 0 | 1                 | Set         |

| 1 | 1 | Х                 | Not allowed |

| S | R | Q | Q(Next) |

|---|---|---|---------|

| 0 | 0 | 0 | 0       |

| 0 | 0 | 1 | 1       |

| 0 | 1 | 0 | 0       |

| 0 | 1 | 1 | 0       |

| 1 | 0 | 0 | 1       |

| 1 | 0 | 1 | 1       |

| 1 | 1 | 0 | X       |

| 1 | 1 | 1 | X       |

| D | Q(Next) |  |

|---|---------|--|

| 0 | 0       |  |

| 1 | 1       |  |

| D | Q | Q(Next) |

|---|---|---------|

| 0 | 0 | 0       |

| 0 | 1 | 0       |

| 1 | 0 | 1       |

| 1 | 1 | 1       |

| T | Q(Next) |  |

|---|---------|--|

| 0 | Q       |  |

| 1 | Q       |  |

| T | Q | Q(Next) |

|---|---|---------|

| 0 | 0 | 0       |

| 0 | 1 | 1       |

| 1 | 0 | 1       |

| 1 | 1 | 0       |

| J | K | Q <sub>next</sub> | Comment   |

|---|---|-------------------|-----------|

| 0 | 0 | Q                 | No change |

| 0 | 1 | 0                 | Reset     |

| 1 | 0 | 1                 | Set       |

| 1 | 1 | Q                 | Toggle    |

| J | K | Q | Q(Next) |

|---|---|---|---------|

| 0 | 0 | 0 | 0       |

| 0 | 0 | 1 | 1       |

| 0 | 1 | 0 | 0       |

| 0 | 1 | 1 | 0       |

| 1 | 0 | 0 | 1       |

| 1 | 0 | 1 | 1       |

| 1 | 1 | 0 | 1       |

| 1 | 1 | 1 | 0       |

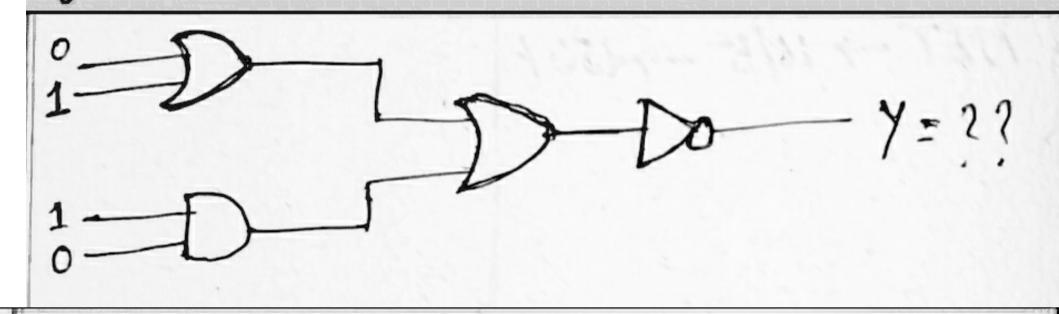

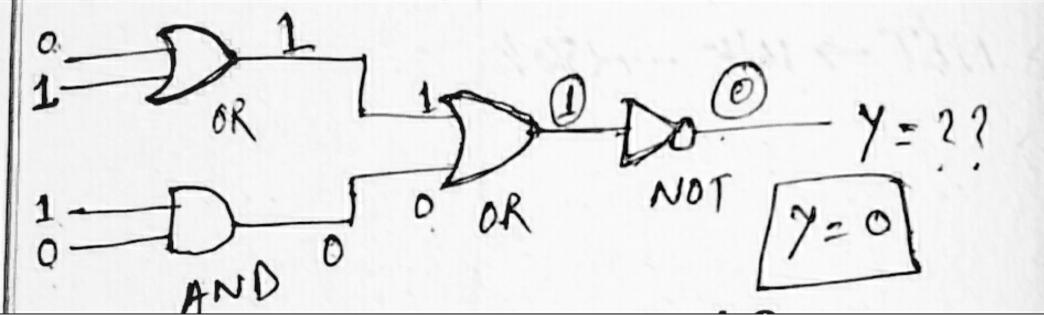

# LOGIC GATES PROBLEM

# Q) Find out the value of Y=?

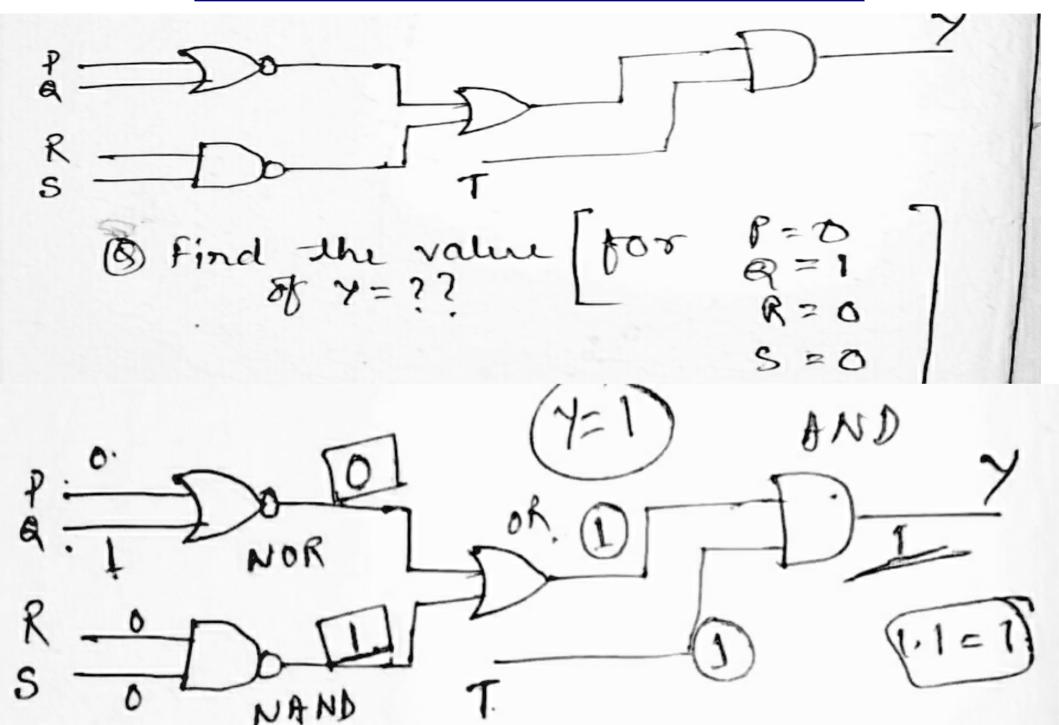

# LOGIC GATES PROBLEM

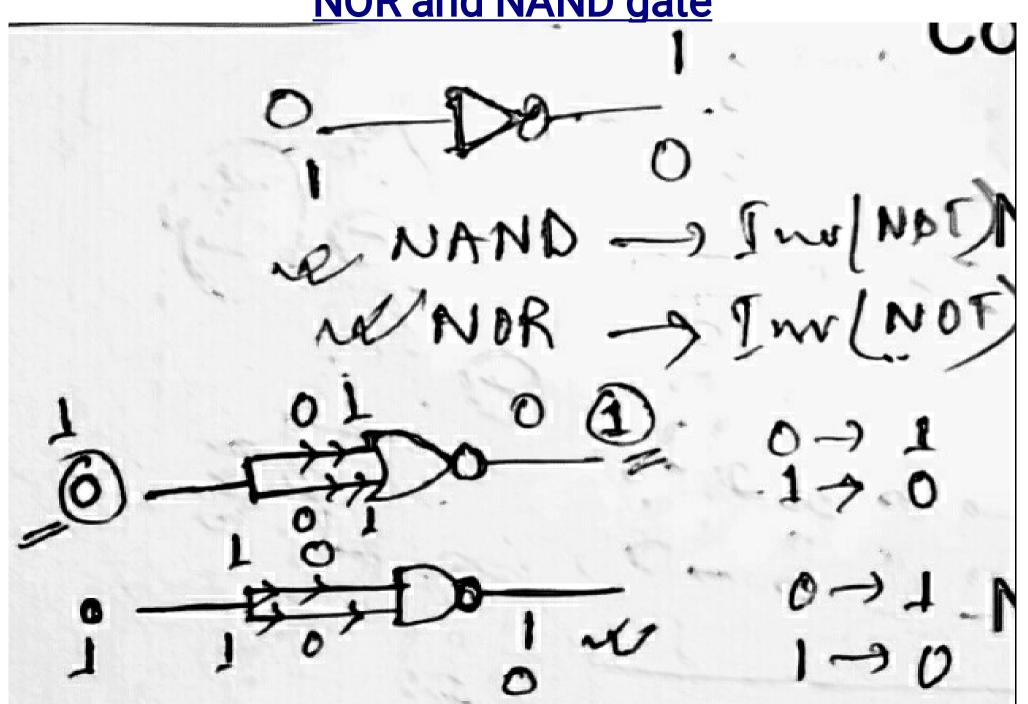

Construction of NOT gate by using NOR and NAND gate